CS 공부

캐시 메모리 본문

캐시 메모리란

캐시 메모리는 CPU의 처리속도와 주기억장치의 접근 속도 차이를 줄이기 위해 사용하는 고속 Buffer Memory이다. CPU와 메인 메모리 사이에 존재한다고 말할 수 있는데, CPU내에 존재할 수도 있고 역할이나 성능에 따라서는 CPU밖에 존재할 수도 있다

빠른 CPU의 처리속도와 상대적으로 느린 메인 메모리에서의 속도의 차이를 극복하는 중간 버퍼 역할을 한다. 쉽게 표현하면 CPU는 빠르게 일을 진행하고 있는데, 메모리에서 데이터를 가져오고 가져가는데 느려서 중간에 미리 CPU에 전달될 데이터를 들고 서 있는 형태라고 말할 수 있다.

캐시메모리의 특징

- 캐시는 주기억장치와 CPU사이에 위치하며, 자주 사용하는 프로그램과 데이터를 기억

- 캐시 메모리는 메모리 계층 구조에서 가장 빠른 소자이며, 처리속도가 거의 CPU의 속도와 비슷할 정도의 속도를 가지고 있다.

- 캐시메모리를 사용하면 주 기억장치를 접근하는 횟수가 줄어들어 컴퓨터의 처리속도가 향상된다.

- 캐시 주소표는 검색시간을 단축시키기 위해 주로 연관기억장치를 사용한다.

- 캐시의 크기는 보통 수십 KByte ~ 수백 KByte이다.

- 캐시 메모리 교체전략은 메모리 페이지 교체 알고리즘을 보면된다.

캐시의 계층적 구조

CPU 사양을 보면 L1 캐시 / L2 캐시 등이 존재한다. 이 캐시 메모리에 따라서 CPU 성능의 우열을 판가름할 수도 있다. 캐시 메모리가 많으면 성능적으로 유리하다고 말할 수 있다.

CPU에는 이러한 캐시 메모리가 2~3개 정도 사용된다. 이를 L1, L2, L3 캐시 메모리라 하며, 여기서 L은 'Level'을 의미한다.

L1캐시는 일반적으로 CPU 칩안에 내장되어 데이터 사용/참조에 가장 먼저 사용된다

L1캐시는 보통 8~256KB 정도의 용량으로 CPU가 가장 빠르게 접근하게 되며 여기서 데이터를 찾지 못하면 L2 캐시메모리로 넘어간다.

L2 캐시 메모리는 용도와 역할은 L1 캐시와 비슷하지만 속도는 그보다 느리다. 일반적으로 256KB~15MB 정도가 사용된다. L2 캐시는 CPU 회로판에 별도의 칩으로 내장된다.

L3 캐시 메모리도 동일한 원리로 작동한다. 웬만한 프로세서에서는 L3 캐시 메모리를 달고있지 않다. L2 캐시로 충분히 커버할 수 있기 때문이다. intel core2 duo나 quad에는 L3 캐시가 없지만, 코어 i7에는 8MB를 달아뒀다. L1/L2 캐시 메모리 정도만 CPU 성능에 직접적인 영향을 미치기에 L3 캐시는 크게 신경쓰지 않는것이 일반적인 추세다. L3 캐시는 CPU가 아닌 메인보드에 내장되는 경우가 더 많다.

캐시메모리의 성능

캐시 적중(hit): 프로세서가 참조하려는 정보가 있을 때

캐시 실패(miss): 프로세서가 참조하려는 정보가 없을 때

캐시 메모리의 적중 성공 여부는 지역성 원리에 달려있다.

물론 지역성은 경향에 대한 것이므로 항상 캐시의 높은 적중률을 보장해주지는 않는다.

히트율: 히트수 / CPU에 의한 메모리 참조의 총 수

지역성의 종류

시간적 지역성: CPU가 한 번 참조한 데이터는 다시 참조할 가능성이 높다.

공간적 지역성: CPU가 참조한 데이터와 인접한 데이터 역시 참조될 가능성이 높다.

순차적 지역성: 분기가 발생하지 않는 한 명령어는 메모리에 저장된 순서대로 인출/실행된다.

참조의 지역성: 동일한 값 또는 해당 값에 관계된 스토리지 위치가 자주 액세스되는 특성으로, 지역성의 원리(principle of locality)라고도 불린다.

인출 방식 (Fetch Algorithm)

요구 인출(Demand Fetch) : 필요 시 요구하여 인출하는 방식

선 인출(Pre-Fetch) : 예상되는 데이터를 미리 인출하는 방식

매핑

CPU가 메모리 주소를 사용하여 메모리로 데이터를 받으려고 할 때 메모리 주소를 보내는데 CPU가 쓰는 주소는 가상 메모리 주소로 메모리 입장에서는 알아들을 수가 없다. 따라서 중간에 메모리 관리 장치(MMU)가 가운데에서 변역을 하여 메모리가 알아 먹을 수 있는 물리 주소로 변환해 준다. 이것이 매핑 프로세스이다,

매핑 프로세스는 주기억장치로부터 캐시 메모리로 데이터를 전송하는 방법을 말하는 것으로 3가지 방법이 있습니다.

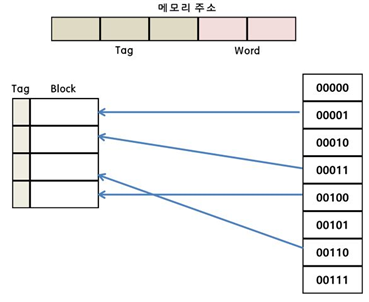

직접 매핑(direct Mapping)

직접 매핑은 위의 사진처럼 캐시에 저장된 데이터들은 메인 메모리에서와 동일한 배열을 가지도록 매핑하는 방법을 말한다. 즉 주기억장치의 블록들이 지정된 한 개의 캐시 라인으로만 사상될 수 있는 매핑 방법이다.

우선 메인 메모리에서 캐시로 데이터를 저장할 때 참조의 지역성 때문에 한번 퍼낼 때 인접한 곳까지 한꺼번에 캐시 메모리에 저장하고 이 때 단위를 블록(Block)이라고 한다. 그리고 캐쉬는 메인 메모리의 몇 번째 블록인지를 알려주는 태그(Tag)도 함께 저장한다.

메모리 주소 중에 가장 뒷부분(붉은색)은 블럭의 크기를 의미한다.

지금 블럭의 크기가 4이므로 뒤의 두자리를 사용하여 블럭의 크기를 표현하였다.

그리고 이 영역은 블럭에 몇 번째에 원하는 데이터가 있는지 보여주는 지표가 되어 준다.

같은 라인에 위치하는 데이터는 파란색 색칠한 영역에 의하여 구별이 가능하다.

예를 들면 메모리에 첫번째 요소 00000과 다섯번재 주소 00100은 캐시내에 같은 위치에 자리잡고 있어서 구별이 필요한데, 앞의 세자리 000과 001로 구별을 할 수 있다.

이와 같은 요소의 활용은 캐시 메모리에 저장된 데이터 중 내가 원하는 것이 있는지 없는지 확인이 가능하다.

캐시의 태그와 주소상의 태그가 동일한지 확인한 후 같으면 붉은 영역을 통해 데이터를 읽는다.

만일 태그가 다르다면 메모리에서 데이터를 가지고 온다.

이와 같은 방식을 사용하기 때문에 매우 단순하고 구현하는 비용이 적게들며 탐색이 쉽다는 장점이 있다.

하지만 적중률(Hit ratio)가 낮다는 단점이 있다.

반복문을 사용할 건데 같은 라인의 00000을 불렀다가 그 다음엔 00100을 부른다면 캐시에 빈번하게 변경이 발생할 수 있기 때문이다.

어소시에이티브 매핑(Associative Mapping)

직접 매핑 방식의 단점을 보완한 방식이다.

캐시에 저장된 데이터들은 메인 메모리의 순서와는 아무런 관련이 없다.

이런 같은 방식을 사용하기 때문에 캐시를 전부 뒤져서 태그가 같은 데이터가 있는지 확인해야한다.

따라서 적중률이 높다는 장점이 있지만, 모든 태그들을 병렬로 검사하기 때문에 복잡하고 비용이 높다는 단점(시간이 오래걸림) 때문에 거의 사용하지 않는다.

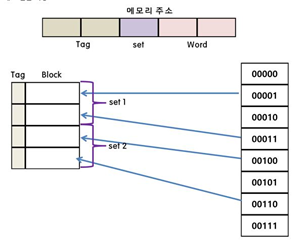

세트-어소시에이티브 매핑(Set-Associative Mapping)

직접 매핑의 단순한 회로와 연관 매핑의 적중률 두 개의 장점만을 취하기 위해서 만들어진 방식이다.

set을 먼저 설정하고 -> 그 다음 어느 블록에 들어갈 것인지 결정 (ex : 4-way면 4개 블록중 하나)

각각의 라인들은 하나의 세트에 속해 있다.

세트 번호를 통해 영역을 탐색하므로 연관 매핑의 병렬 탐색을 줄일 수 있다.

그리고 모든 라인에 연관 매핑처럼 무작위로 위치하여 직접매핑의 단점도 보완하였다.

세트 안의 라인 수에 따라 n-way 연관 매핑이라고 한다.(ex: 2-way집합 연관 사상)

쓰기 정책 (Write Policy)

Write-Through

주기억 장치와 캐시에 동시에 쓰는 방식

캐시에 쓰기 동작이 이루어질 때마다 캐시 메모리와 주기억장치의 내용을 동시에 갱신하므로 쓰기 동작에 걸리는 시간이 가장 길다. Wirte Through 방식 역시 갱신된 캐시와 주기억장치의 데이터는 동일하지만 타 캐시의 데이터가 무효가 되므로 캐시 일관성 문제가 발생할 수 있다.

Write-Back

캐시에 쓰기 동작이 이루어지는 동안은 캐시의 내용만이 갱신되고, 캐시의 내용이 캐시로부터 제거될 때 주기억장치에 복사된다.

Write-Once

캐시에 쓰기 동작이 이루어질 때 한번만 기록하고 이후의 기록은 모두 무시한다.

캐시의 일관성

같은 공유 메모리 방식의 병렬 컴퓨터에서 주기억 장치(공유 메모리)와 캐시에 저장된 데이터가 달라지는 현상.

캐시 내의 데이터가 변경되면 주기억장치내의 해당 단어 뿐 아니라 다른 캐시 내의 그 단어도 무효가 된다.

캐시 일관성 유지방식

소프트웨어 방식

컴파일러와 OS를 이용. 잠재된 문제를 검출하는 오버헤드가 run time에서 compile time으로 이동하고, 설계 복잡도가 하드웨어에서 소프트웨어로 이동하는 것이 장점

반면 compile time에 문제를 검출해야 하므로 캐시 이용률이 저하됨.

하드웨어 방식

캐시 일관성 프로토콜이라고도 하며, 잠재적인 불일치 조건들이 run time에 동적으로 검출

소프트웨어 방식에 비해 캐시 사용률이 좋으며, 프로그래머와 컴파일러에 투명하므로 소프트웨어 개발 부담을 줄임

일반적으로 디렉토리 프로토콜(directory protocol)과 스누피 프로토콜(snoopy protocol)으로 나뉜다.

캐시의 기본 구성과 동작

CPU는 데이터를 요청할 때마다 캐시 메모리에서 해당 데이터의 존재 여부를 확인한다.

따라서 캐시 메모리는 요청받은 데이터를 탐색하는 기능이 필요하다.

캐시 메모리는 데이터를 관리하기 위해 데이터 메모리와 태그 메모리를 사용한다.

블록 : 데이터의 기본 단위인 워드의 집합

데이터 메모리 : 메모리의 데이터들이 저장된 블록으로 구성되어 있다.

태그 메모리 : 데이터 메모리의 블록을 탐색할 정보를 포함한다.

태그 메모리의 엔트리는 데이터 메모리 블록과 쌍을 이루면서 태그, 유효 비트, 갱신 비트를 포함한다. 또한 CPU 주소와 태그를 비교하는 비교기를 가지고 있다.

태그(tag) : CPU가 요청한 데이터를 탐색하는데 사용할 주소의 일부. 캐시 블록 주소에서 인덱스로 사용되지 않는 부분이다.

유효 비트(valid bit) : 캐시 블록이 유효한 데이터인지 나타낸다.

갱신 비트(dirty bit) : 캐시로 블록을 가져온 후 CPU가 블록을 수정했는지 나타낸다.

기본적인 동작의 흐름

CPU가 캐시에 주소 전송 > 태그 메모리 탐색 > 일치하는 태그 발견 (hit) > 블록 상태 갱신(필요할 경우) >데이터 메모리에서 블록 추출 > 요청받은 데이터 선택 > 캐시가 CPU에 데이터 전송

CPU가 캐시에 주소 전송 > 태그 메모리 탐색 > 일치하는 태그 없음(miss) > 주소를 메모리로 전송해 대응하는 블록을 캐시에 저장 > 요청받은 데이터 선택 > 캐시가 CPU에 데이터 전송

참고

https://jwprogramming.tistory.com/18

https://zion830.tistory.com/46

https://coding-factory.tistory.com/357

https://com-study.tistory.com/10?category=993858

'CS공부 > 컴퓨터 구조' 카테고리의 다른 글

| ARM (0) | 2021.07.29 |

|---|---|

| 패리티 비트 & 해밍 코드 (0) | 2021.07.29 |

| 고정 소수점 & 부동 소수점 (0) | 2021.07.29 |

| CPU의 작동 (0) | 2021.07.26 |

| 컴퓨터의 구조 (0) | 2021.07.26 |